Computer System Architecture - Central Processing Unit

- A

Hard wired control, vertical microprogramming, horizontal micro-programming.

- B

Hard wired control, horizontal microprogramming, vertical micro-programming.

- C

Horizontal micro-programming, vertical microprogramming, Hard wired control.

- D

Vertical micro-programming, horizontal microprogramming, hard wired control.

- Option : B

- Explanation : Hardwired control is the fastest. Since horizontal microprogramming involves lesser number of instructions, it is faster than vertical microprogramming.

- Option : A

- Explanation : Control memory processor has 26 bit microinstruction divided into three field microoperation field is 13.

So, next address field (X) = 10

MAX select field = 3

Size of control = 210 = 1024

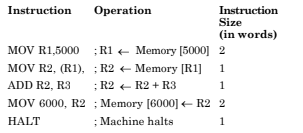

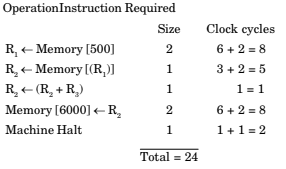

Consider the following assembly language program

for a hypothetical processor. A, B and C are 8 bit

registers. The meanings of various instructions are

shown as comments.

MOV B, # 0 ; B ⇽ 0

MOV C, # 8 ; C ⇽ 8

Z : CMP C, # 0 ; Compare C with 0

JZ X ; Jump to X if 0 flag is set

SUB C, # 1 ; C ⇽ C – 1

RRC A, # 1 ; Rotate right A through carry by

one bit

JC Y ; Jump to Y if any carry flag is set

JMP Z ; Jump to Z

Y : ADD B, # 1 ; B ⇽ B + 1

JMP Z ; Jump to Z

X

Consider the following assembly language program

for a hypothetical processor. A, B and C are 8 bit

registers. The meanings of various instructions are

shown as comments.

MOV B, # 0 ; B ⇽ 0

MOV C, # 8 ; C ⇽ 8

Z : CMP C, # 0 ; Compare C with 0

JZ X ; Jump to X if 0 flag is set

SUB C, # 1 ; C ⇽ C – 1

RRC A, # 1 ; Rotate right A through carry by

one bit

JC Y ; Jump to Y if any carry flag is set

JMP Z ; Jump to Z

Y : ADD B, # 1 ; B ⇽ B + 1

JMP Z ; Jump to Z

X