Computer System Architecture - Memory Hierarchy

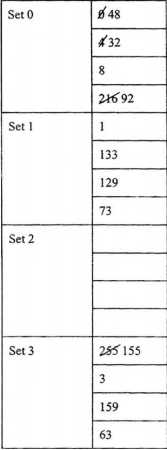

Consider a computer with a 4-ways set-associative mapped cache of the following characteristics : a total of 1 MB of main memory, a word size of 1 byte, a block size of 128 words and a cache size of 8 KB.

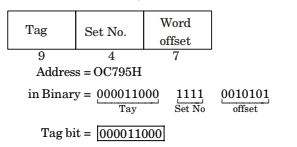

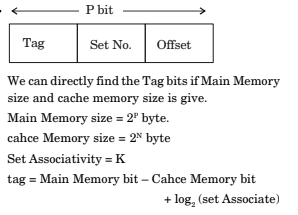

46. The number of bits in the TAG, SET and WORD fields, respectively are :

- Option : D

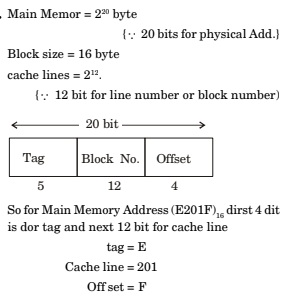

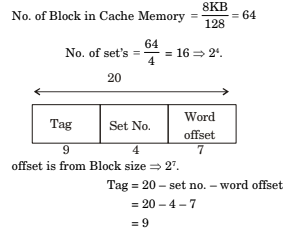

- Explanation : Size of main Memory = 1 MB = 220 byte

Size of cache Memory = 8 KB

Block Size = 128 words = 27

Consider a computer with a 4-ways set-associative mapped cache of the following characteristics : a total of 1 MB of main memory, a word size of 1 byte, a block size of 128 words and a cache size of 8 KB.