PREVIOUS YEAR SOLVED PAPERS - GATE 2019

- Option : D

- Explanation : Given cache block size is 16 bytes, so block or word offset is 4 bits. Fully associative cache of size 16 kB, so line offset should be,

= cache size / block size

= 16 kB / 16 B = 1 k

= 1024

= 10 bits Line or Index Offset

Tag bit size would be,

= processor address size - (line offset + word offset)

= 32 - 10 - 4

= 18 bits tag size

Since, there no option matches, but if we assume that Line Offset is a part of Tag bits, therefore,

Tag bits = 18+10 = 28 bits

Line or Index offset = 0 bits (since fully associative cache memory),

Word or block offset = 4 bits

32 - bit Tag offset Word offset 28 bit 4 bit

14. In 16-bit 2’s complement representation, the decimal number −28 is:

- Option : C

- Explanation : A = {(x, X), x ∈ X and X ⊆ U}

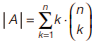

The number of k element subsets of a set U with n elements =

= nCk'

The number of possible ordered pairs (x, X) where x ∈ X is then 2n-1 Sets are possible so for all n elements total n ⋅ 2n-1 number of order pairs are possible.

thus statement I is true and

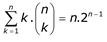

But since by the combinatoric identity

= nCk'

The number of possible ordered pairs (x, X) where x ∈ X is then 2n-1 Sets are possible so for all n elements total n ⋅ 2n-1 number of order pairs are possible.

thus statement I is true and

But since by the combinatoric identity

statement II is identity similar to statement I thus also true.

statement II is identity similar to statement I thus also true.

Which of the following is correct?

Which of the following is correct?