Gate2020 cs Q51

- Option : B

- Explanation : Non-pipeline

Clock frequency = 2.5 GHz.

Cycle time = 1/2.5 GHz = 0.4ns

Given, CPI = 5

So, ETnon-pipe = CPI × Cycle time

= 5 × 0.4 ns = 2 ns

Pipeline:

Clock frequency = 24 GHz

Cycle time = 1/2 GHz = 0.5ns

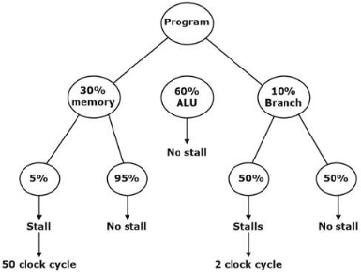

∴ Number of stalls/instruction = 0.3 × 0.05 × 50 + 0.1 * 0.5 × 2

= 0.85

Avg. instruction ETpipe = (1 + No. of stall instruction) * cycle time

= (1 + 0.85) × 0.5 ns = 0.925 ns

∴ Number of stalls/instruction = 0.3 × 0.05 × 50 + 0.1 * 0.5 × 2

= 0.85

Avg. instruction ETpipe = (1 + No. of stall instruction) * cycle time

= (1 + 0.85) × 0.5 ns = 0.925 ns