Central Processing Unit Q.19

- Option : B

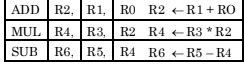

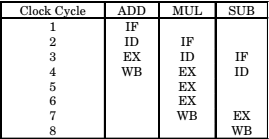

- Explanation : For each of the three instruction four stages will be

there. Since ,it is a pipelined processor, so one instruction may be fetched while other is being decoded

or executed or written back action performed in

each clock cycle may be represented as

Only, two instructions cannot be executed simultaneously.