Pipeline and Vector Processing Q.23

- Option : A

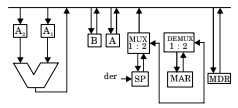

- Explanation : Push ‘r’ consist of following operations :

M[SP ]!R

SP!SP-1

‘r’ is stored at memory at address stack pointer currently is, this take 2 clock cycles

SP is then decremented to point to next top of stack