PREVIOUS YEAR SOLVED PAPERS - GATE 2020

- Option : A

- Explanation : No. of relation on A = 29 No. of reflexive relation on A = 2(n2-n) = 2(32-3) = 26 ∴ Probability (reflexive) = 26 / 29 = 1/8 = 0.125

- Option : B

- Explanation : Cache Memory = 1 MB Word size = 64 bit = 8 B Block size = 256 B Hit rate, x = 0.94 miss rate= 1-x = 0.06 Cache access time, Tc = 3ns Number of words / Block = 256/8 = 32 Using Hierarchical Approach, Tavg= ( x.Tc ) + (1-x)[ Tc + 1st word access time + remaining word access time] Tavg = (0.94 × 3) + (1 – 0.94) [3 + 20 + (31 × 5)] Tavg = 13.5 ns

- Option : D

- Explanation : Byte addressable 1 KB RAM ⇒ 210 bytes m = 10 n = 2m m = 10, n = 1024 so, m+n= 1024+ 10 = 1034

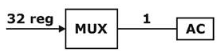

MUX: 2n inputs, n selection lines, 1 o/p

2n = 32 ⇒ n = 5

MUX: 2n inputs, n selection lines, 1 o/p

2n = 32 ⇒ n = 5